本项目共设计了两块板子,一块采用RTL-8201F百兆PHY芯片,另一块采用RTL-8211F千兆PHY芯片,两者配置略有不同,基本原理相通。项目设计刚好采用了两种不同的方式,因此其配置方式可以互相参考。

预备知识

要使用以太网功能,需要有一个MAC层芯片以及一个PHY层芯片,USB有线网卡一般集成了两者因此可以直接使用,而RK3568则集成MAC层的功能,因此仅需要额外搭配一个PHY层芯片,即可实现以太网通信。PHY芯片需要被提供一个25Mhz工作时钟信号。除此之外MAC层芯片和PHY层芯片之间需要有一个同步时钟信号,可以由MAC给到PHY,亦可以由PHY给到MAC,由硬件电路设计及PHY芯片决定。

RTL-8201F百兆PHY芯片配置

原理图分析

LED1/PHYAD1(芯片第25脚):被拉低,因此地址位1为0LED0/PHYAD0(芯片第24脚):被拉高,因此地址位0为1PHY地址:从高到低[1:0],因此地址位为0b01

RXD3/CLK_CTL(芯片第12脚):被拉高,因此时钟方向为MAC(output)给PHY(input)RXDV(芯片第8脚):被拉高,因此使用RMII通信模式

RXEN/FXEN(芯片第28脚):被拉低,因此是UTP(双绞线)模式

配置要点

复位脚(RSET):低电平有效,默认拉高

项目百兆PHY工作时钟25Mhz由RK3568给出

项目百兆PHY同步时钟由MAC给到PHY

GMAC1有M0或M1两个通道,注意选择

DTS配置

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43 44 45

&pinctrl { gmac1 { gmac1_reset: gmac1-reset { rockchip,pins = <3 RK_PD1 RK_FUNC_GPIO &pcfg_pull_up > ; }; }; }; &gmac1 { phy-mode = "rmii" ; # RMII工作模式 clock_in_out = "output" ; # 同步时钟方向为MAC->PHY(这里output相对mac来说) # 由MAC给出同步时钟要额外分配<&cru CLK_MAC1_OUT>及<25000000> assigned-clocks = <&cru SCLK_GMAC1_RX_TX> , <&cru SCLK_GMAC1> , <&cru CLK_MAC1_OUT> ; assigned-clock-parents = <&cru SCLK_GMAC1_RMII_SPEED> ; assigned-clock-rates = <0 > , <50000000 > , <25000000 > ; snps,reset-gpio = <&gpio3 RK_PD1 GPIO_ACTIVE_LOW> ; snps,reset-active-low ; snps,reset-delays-us = <200000 20000 300000 > ; pinctrl-names = "default" ; pinctrl-0 = <&gmac1m1_miim &gmac1m1_clkinout &gmac1m1_rx_bus2 &gmac1m1_tx_bus2 &gmac1m1_rx_er ð1m1_pins # PIN脚使能25 Mhz工作时钟功能,若使用外部晶震,可以删掉 &gmac1_reset > ; tx_delay = <0x30 > ; rx_delay = <0x10 > ; phy-handle = <ð1 > ; status = "okay" ; }; &mdio1 { eth1: phy@1 { compatible = "ethernet-phy-ieee802.3-c22" ; reg = <0x1 > ; clocks = <&cru CLK_MAC1_OUT> ; # 使用MAC给出的时钟 }; };

遇到的问题

RTL-8211F千兆PHY芯片配置

原理图分析

RXCTL/PHYAD2(芯片第26脚):被拉低,因此地址位2为0RXC/PHYAD1(芯片第27脚):被拉低,因此地址位1为0RXD3/PHYAD0(芯片第22脚):被拉高,因此地址位0为1PHY地址:从高到低[2:0],因此地址位为0b001

LED0/CFG_EXT(芯片第32脚):被拉高,因此外置电源域

LED1/CFG_LDO0(芯片第33脚):被拉低,外置电源域3.3V,因此对应VCCIO配成3.3V

LED2/CFG_LDO1(芯片第34脚):被拉低,外置电源域3.3V,因此对应VCCIO配成3.3V

配置要点

复位脚(RSET):低电平有效,默认拉高

项目千兆PHY工作时钟25Mhz由外部晶震给出

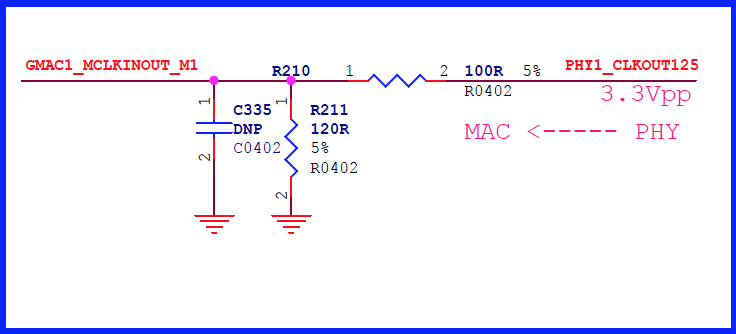

项目千兆PHY同步时钟只能由PHY给到MAC

GMAC1有M0或M1两个通道,注意选择

DTS配置

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43 44 45 46 47 48 49 50

&pinctrl { gmac1 { gmac1_reset: gmac1-reset { rockchip,pins = <3 RK_PD1 RK_FUNC_GPIO &pcfg_pull_up > ; }; }; }; # 定义PHY给出的同步时钟125Mhz &gmac1_clkin { clock-frequency = <125000000 > ; }; &gmac1 { phy-mode = "rgmii" ; clock_in_out = "input" ; 同步时钟方向为PHY->MAC snps,reset-gpio = <&gpio3 RK_PD1 GPIO_ACTIVE_LOW> ; snps,reset-active-low ; snps,reset-delays-us = <0 20000 100000 > ; # SCLK_GMAC1来自外部时钟&gmac1_clkin assigned-clocks = <&cru SCLK_GMAC1_RX_TX> , <&cru SCLK_GMAC1> ; assigned-clock-parents = <&cru SCLK_GMAC1_RGMII_SPEED> , <&gmac1_clkin > ; assigned-clock-rates = <0 > , <125000000 > ; pinctrl-names = "default" ; pinctrl-0 = <&gmac1m1_miim &gmac1m1_tx_bus2 &gmac1m1_rx_bus2 &gmac1m1_rgmii_clk &gmac1m1_rgmii_bus &gmac1m1_clkinout &gmac1_reset > ; tx_delay = <0x42 > ; # 见后文Delayline配置 rx_delay = <0x2c > ; # 见后文Delayline配置 phy-handle = <ð1 > ; status = "okay" ; }; &mdio1 { eth1: phy@1 { compatible = "ethernet-phy-ieee802.3-c22" ; reg = <0x1 > ; }; };

Delayline配置

按照RK的说法:“只要有硬件的差别,都需要重新做一次delayline的配置,否则会影响千兆以太网的配置。”因此针对不同的板子都需要重新做该配置。

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22

cd /sys/devices/platform/fe010000.ethernet/echo 1000 > phy_lb_scandmesg | grep suitable > [ 118.289125] Find suitable tx_delay = 0x42, rx_delay = 0x2c echo 0x3f 0x2c > rgmii_delaylinecat rgmii_delayline> tx delayline: 0x3f, rx delayline: 0x2c echo 1000 > phy_lbdmesg | grep loopback > [ 221.940497] PHY loopback speed set to 1000 > [ 222.670675] PHY loopback: PASS

遇到的问题

PHY已正确识别,但是配置上IP地址后无法通信,日志无异常,经排查125M同步时钟信号被下拉到1.8V,去掉图中R211电阻后PHY可以正常工作

PHY状态灯

一般需要根据PHY的Datasheet修改对应的寄存器来配置项目所需的状态灯。这里提供一个适用于kernel-4.19的PHY状态灯补丁 (基于RK的kernel-4.4版本并加入RTL-8211F芯片支持)。

调试命令

1 2 3 4 5 6 7 8 9 10 11 12 13 14

cd /sys/devices/platform/fe010000.ethernet/mdio_bus/stmmac-1/stmmac-1:01cat phy_idcat phy_registersecho 31 0x0d04 > phy_registers

测试工具

参考文档

RKDocs/common/GMAC/Rockchip_Developer_Guide_Linux_GMAC_Mode_Configuration_CN.pdf

RKDocs/common/GMAC/Rockchip_Developer_Guide_Linux_GMAC_RGMII_Delayline_CN.pdf